# Multi-Standard Processing using DAB and 802.11p Carina Schmidt-Knorreck<sup>1</sup>, Matthias Ihmig<sup>2</sup>, Raymond Knopp<sup>1</sup>, Andreas Herkersdorf<sup>2</sup>

<sup>1</sup>Mobile Communications Department, EURECOM, Sophia Antipolis, France

## <sup>2</sup>Institute for Integrated Systems, TUM, Munich, Germany

### **1. Introduction**

#### Situation

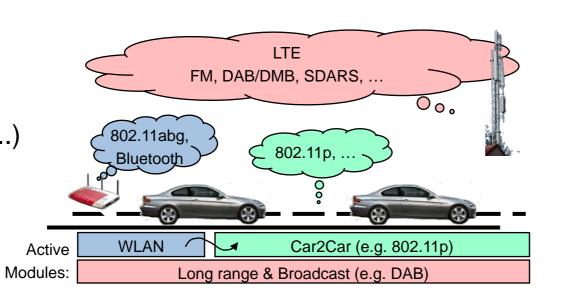

- Increasing number of wireless standards for mobile environment requires new design approach for electronic control units (ECU)

- Multiple wireless standards must run in **parallel**

#### Approach

Software Radio provides flexibility for upgrades and configurations

#### Challenge

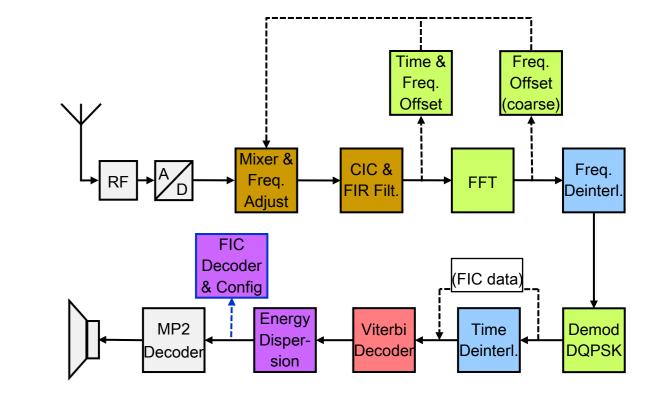

- SDR Platform is **MPSoC system** with accelerators for special operations (Vector Operations, FFT, Channel Decoder, ...)

- **PROTON/PLATA Project: Parallel processing** of ETSI-DAB and IEEE-802.11p by sharing the same hardware resources

- Time-sharing between multiple standards while meeting latency and processing requirements

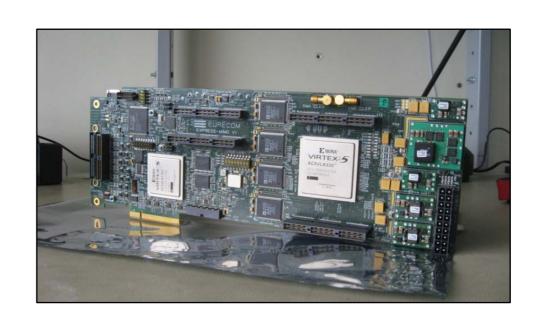

- The **OpenAirInterface Platform** is a generic prototype architecture for multimodal applications

- Support of a high number of different standards: 3GPP, UMTS (TDD), WLAN 802.11a/g/p, WIMAX, GSM, DAB, LTE, ...

- Advantages include effective use of the spectrum, mobility, increased network capacity, maintenance of cost reduction, faster deployment of new standards, improvement of existing standards and faster development of new services

- **Baseband processing** operations are split over independent IP Blocks that are controlled by a LEON3 microcontroller

## 3. 802.11p vs DAB

#### **Properties 802.11p receiver**

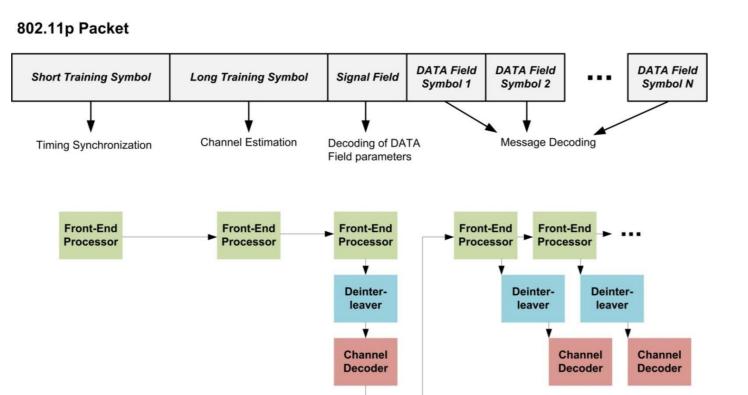

- Packet oriented standard

- Between 480 and 109680 samples per packet (correspond to 48us to 10968us for 10MHz channel spacing); number of samples depends on the modulation scheme

- Processing Time of one packets depends on packet size, modulation scheme, interarrival time

- Strong latency requirements

#### Challenges

- Communication System: Short latency requirements (microseconds) must be satisfied

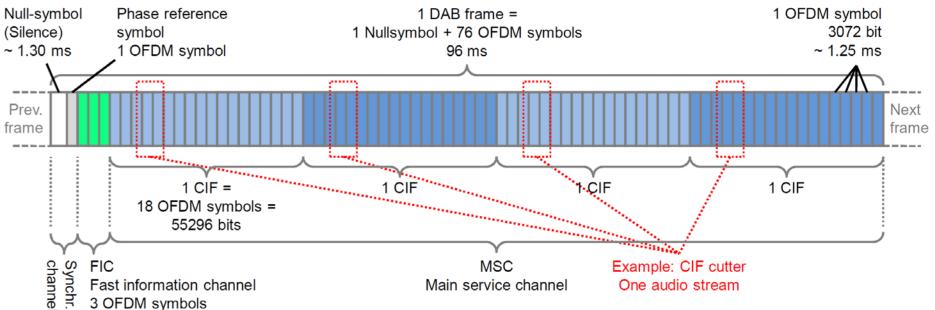

- Broadcast receiver: Large symbols and vectors cause long execution time

- Macro Operations (FFT, Vector Operations, Interleaver, ...) cannot be interrupted

- → Sophisticated timing-aware scheduling is required

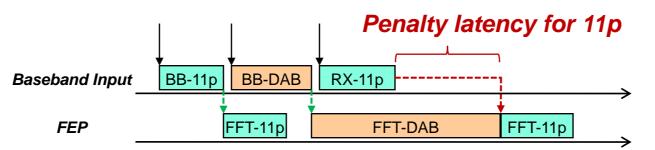

## **4. Timing Analysis**

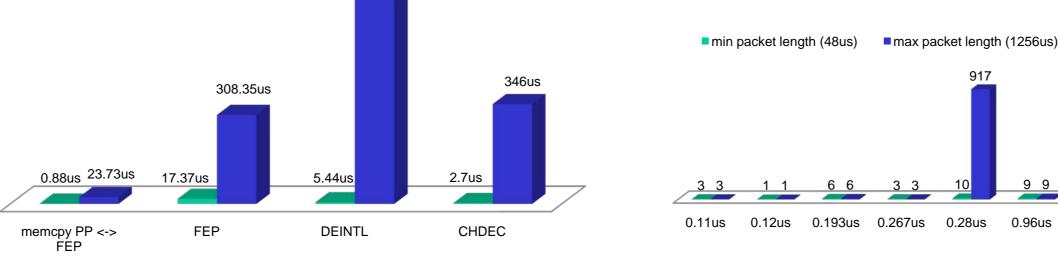

#### **IEEE 802.11p**

- FEP Macro execution time varies from 0.11us to 0.96us

- Due to strong latency requirements, grouping of Vector Operations

Continuous data stream

**802.11p Runtime Distribution**

FEP (64 QAM, rate 3/4)

Deterministic timing & processing

## **5. Conclusions and Future Work**

#### Conclusions

- Latency requirements fulfilled if only one standard is processed

- Critical processing block: Front-End Processor (FFT cannot be split

- in the Front-End Processor (FEP) recommended

- $\rightarrow$  less time-consuming memcopy required

- The processing times for the IP Blocks include the memory transfer times as the IP Blocks are not available for DAB operations during this time

- Scheduling algorithm has to consider

- The strong latency requirements of 802.11p

- That each splitting of operations requires additional processing time for context saving

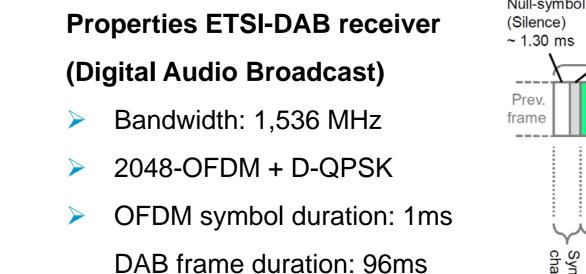

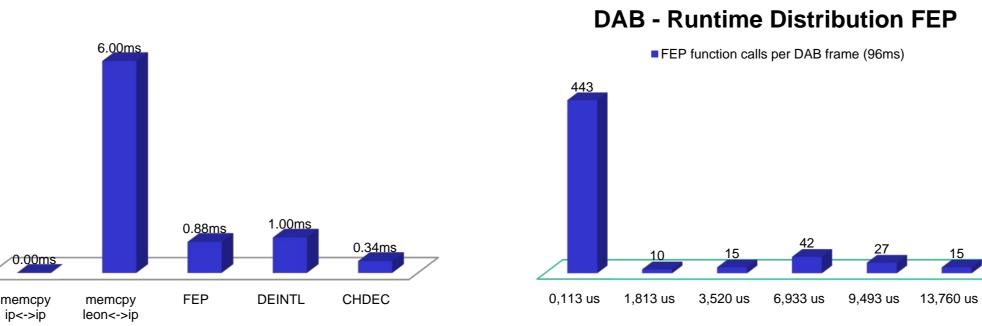

#### **ETSI-DAB**

- FEP Macro execution time varies from 0.14us to 13us

- Longest functions are vector operations; they can be split arbitrarily

- Currently: save context after each macro operation

- $\rightarrow$  time-consuming memcopy required

- FFT (9.49us) cannot be easily split

**IP Block Utilization for different packet**

lengths (64 QAM, rate 3/4)

max packet length (1256us)

731.7us

min packet length (48us)

#### **Future Work**

- Investigation in a timing-aware dynamic scheduler to solve latency problem

- Dynamic splitting of long vector operations into several shorter

operations

EURECOM – 2229 Route des Crêtes – BP 193 F-06904 Sophia Antipolis cedex, www.eurecom.fr

Institute for Integrated Systems, Arcisstrasse 21, D-80290 Munich **BMW Group**, Research and Technology Hanauer Str. 46, D-80992 Munich